|

[Назад] [Содержание] [Вперед]

══════════════════════════════════════════════════════════════════════════ Глава 1. Введение в описание процессора i486(TM). -------------------------------------------------------------------------- Процессор i486 обеспечивает наивысшую скорость выполнения прикладных программ для DOS, OS/2, Windows и UNIX System V/386. Он на 100% программно совместим с микропроцессорами 386(ТМ) DX & SX. Один миллион транзисторов объединенной кэш-памяти (сверхбыстрой оперативной памати), вместе с аппаратурой для выполнения операций с плавающей запятой и управлением памяти на одной микросхеме, тем не менее поддерживают программную совместимость с предыдущими членами семейства процессоров архитектуры 86. Часто используемые операции выполняются за один цикл, что сравнимо со скоростью выполнения RISC-команд. Восьмикилобайтный унифицированный кэш для кода и данных, соединенный с шиной пакетного обмена данными со скоростью 80/106 Мбайт/сек при частоте 25/33 Мгерц гарантируют высокую производительность системы даже с недорогими дисками (DRAM). Новые возможности расширяют многозадачность систем. Новые операции увеличивают скорость работы с семафорами в памяти. Оборудование на микросхеме гарантирует непротиворечивость кеш-памяти и поддерживает средства для реализации многоуровневого кэширования. Встроенная система тестирования проверяет микросхемную логику, кэш-память и микросхемное постраничное преобразование адресов памяти. Возможности отладки включают в себя установку ловушек контрольных точек в выполненяемом коде и при доступе к данным. Возможности процессора i486 включают в себя: - Полная программная совместимость с ЦПУ 386 DX, 386 SX, встроенным 376(TM) процессором, процессорами 80286, 8086 и 8088; - Модуль выполнения команд разработан так, чтобы выполнять часто встречающиеся операции за один цикл; - 32-разрядный процессор для выполнения арифметических и логических операций; - Встроенный модуль обработки арифметических операций с плавающей точкой для поддержки 32, 64, и 80-разрядных форматов, заданных в соответствие со стандартом IEEE 754 (объектно совместимом с 387 (TM) DX и 387 SX арифметическими сопроцессорами); - Внутренняя 8 Кбайтовая кэш-память, которая обеспечивает быстрый доступ к часто используемым данным и операциям; - Сигналы управления шиной для поддержки непротиворечивости кэша в многоза- дачных системах; - Сегментация, одна из форм управления памятью для создания независимых, защищенных адресных пространств; - Постраничное разбиение, одна из форм управления памятью, которая обеспечивает доступ к структурам данных, большим, чем доступное пространство памяти, путем хранения данных частично в памяти, частично на диске; - Перезапускаемые операторы, которые позволяют перезапуск программы после исключения (необходимы для поддержки постраничного доступа к виртуальной памяти); - Конвеерное выполнение команд, перекрывающееся по времени с интерпретацией других команд; - Регистры отладки для аппаратной поддержки контрорльных точек в командах и данных; Процессор i486 совместим на уровне объектных кодов с тремя другими процессорами семейства 386: - Процессор 386 DX (32-разрядная шина данных) - эффективная относительно своей стоимости форма для персональных компьютеров высокого класса и рыночих станций среднего уровня; - Процессор 386 SX (16-разрядная шина данных) - 386-ой процессор, адаптированный для персональных компьютеров среднего класса, для которых существенна высокая цена системы с 32-разрядной шиной. - 376 встроенный процессор (16-разрядная шина данных) - упрощенная форма 386 процессора, оптимизированная для применения в качестве встроенного в систему процессора, такую как контроллеры процессов. Процессору 386 не хватает постраничной организации памяти и совместимости с процессором 8086, обеспечиваемых процессором i486. Процессор 376 значительно дешевле и меньше любого варианта исполнения процессора 386. Режим работы процессора i486 определяет, какие команды и какие архитектурные возможности доступны. Процессор i486 предусматривает три режима выполнения программ: - Защищенный режим использует естественное множество 32-разрядных команд процессора. В данном режиме доступны все команды и все архитектурные возможности. - Режим реальной (прямой) адресации (называемый также "реальным режимом") эмулирует программную среду процессора 8086, с некоторыми дополнительными возможностями (такими, как возможность прервать данный режим). При перезагрузке процессор устанавливается именно в этот режим. - Виртуальный режим 86 (называемый также "режим V86") является другой формой эмуляции режима 8086. В отличие от режима прямой адресации, виртуальный режим 86 совместим с защитой и управлением памятью. Процессор может установить виртуальный режим 86 из защищеного режима, чтобы выполнить программу, написанную для процессора 8086, а затем выйдя из виртуального режима 86 и перейдя в защищенный режим продолжить выполнение программы, которая использует множество 32-разрядных команд. 1.1 Структура данного руководства Эта книга описывает архитектуру процессора i486 в пяти частях: - Часть I - Прикладное программирование. - Часть II - Системное программирование. - Часть III - Численная обработка. - Часть IV - Совместимость. - Часть V - Набор команд. - Приложения. Это деление определяется архитектурой процессора и теми способами, которыми программисты используют данную книгу. Первые три части содержат информацию о назначении различных архитектурных возможностей, развитии терминологии и концепций; описание команд с точки зрения их соотношений со специфифескими задачами и специфическими архитектурными возможностями. Остальные части содержат справочные материалы для программистов, создающих прикладное программное обеспечение для процессора i486. Первые четыре части охватывают режимы работы и механизм защиты процессора i486. Различие между прикладным программированием и системным программированием относится к механизму защиты процессора i486. Одним из назначений механизма защиты является предупреждение столкновений между прикладными программами и операционной системой. По этой причине некоторые регистры и команды недоступны для прикладных программ. Возможности, обсуждаемые в Частях I и III, доступны для прикладных программ; возможности, описанные в Части II, доступны только для программ, выполняемых со специальными привилегиями, или для программ, выполняемых в режимах, где механизм защиты не используется. Возможности, доступные для прикладных программ в защищенном режиме, и для всех программ в виртуальном режиме 8086, одинаковы. Эти возможности описаны в Частях I и III данной книги. Дополнительные возможности, доступные для системных программ в защищенном режиме, описаны в Части II. Часть IV описывает режим прямой адресации и виртуальный режим 86, а также, как выполнять смесь 16-разрядных и 32-разрядных программ. 1.1.1 ЧАСТЬ

I - Прикладное программирование. Эта часть описывает возможности, используемые большинством прикладных программ. В нее не включены описания возможностей, используемых в численных приложениях, которые обсуждаются в Части III. Глава 2 - Основная модель программирования: Дает введение в модели организации памяти. Определяет типы данных. Описывает множество регистров, используемых прикладными программами. Вводит понятие стека. Объясняет операции над строками. Определяет поля команд. Объясняет принципы вычисления адресов. Дает введение в прерывания и исключения с точки зрения того, как они применяются в прикладных программах. Глава 3 - Множество команд для прикладных программ : Рассматриваются команды, обычно используемые в прикладном программировании. Рассматривыемые команды объединены в функционально связанные группы: например, операции над строками объединены в один раздел, в то время как управляющие команды объединены в другом разделе. Основные понятия вводятся до рассмотрения команд. Подробности конкретных команд рассматриваются в Части IV, которая является справочником по всем коммандам процессора. 1.1.2 Часть II - Системное программирование. В данной части описаны возможности, используемые операционной системой, драйверами устройств, отладчиками и другим программным обеспечением, которое поддерживает работу прикладных программ. Некоторая дополнительная информация, относящаяся к системному программированию, представлена в Части III. Глава 4 - Архитектура системы : Описывает возможности процессора i486, используемые системными программистами. Вводит понятия регистров и структур данных процессора i486, которые не описаны в Частях I и III. Описывает системно-ориентированные команды в контексте регистров и структур данных, которые они поддерживают. Ссылается на главы, в которых каждый регистр, структура данных и команда описывается более подробно. Глава 5 - Управление памятью : Описывает возможности структур данных, регистров и команд, которые поддерживают сегментацию. Объясяется, как разработчики систем могут выбирать между несегментированной ("плоской") моделью организации памяти и моделью с сегментацией. Глава 6 - Защита : Обсуждается применение защиты сегментов. Рассматриваются применение правил привилегированности, стековое переключение, оценка достоверности указателя, пользовательский и супервизорский режимы. Обсуждение аспектов защиты при многозадачности отложено до следующей главы. Глава 7 - Многозадачность : Объясняется, как аппаратное обеспечение процессора i486 поддерживает многозадачность с контекстно-зависимым переключением операций и защиту задач от взаимного влияния. Глава 8 - Ввод/Вывод : Описывает возможности ввода/вывода процессора i486, включая команды ввода/вывода; защиту, с точки зрения к ввода/вывода, и битовый массив разрешения ввода/вывода. Глава 9 - Исключения и прерывания : Объясняет основной механизм прерываний процессора i486. Показывает, как прерывания и исключения относятся к защите. Приводится список всех исключений с указанием вызывающих их причин и дополнительной информации, необходимой для обработки и восстановления из каждого исключения. Глава 10 - Инициализация : Определяет состояние процессора после перезагрузки. Объясняет, как задать значения регистров, флагов о структур данных. Показывает, как тестировать память на микросхеме и ассоциативного буфера трансляции. Содержит пример программы инициализации. Глава 11 - Отладка : Описывает, как использовать регистры отладки процессора i486. Глава 12 - Кэширование : Вводит понятие кэширования и описывает специальный механизм, используемый внутренней кэш-памятью процессора i486. Глава 13 - Многозадачность : Объясняет команды и флаги, которые поддерживают множество процессов с разделением памяти. 1.1.3 ЧАСТЬ

III - Численная обработка. Эта часть объясняет возможности арифметики с плавающей точкой для процессора i486. Эти возможности совместимы на уровне объектных кодов с реализацией возможностей, предлагаемых математическими сопроцессорами 387 DX & SX, используемыми вместе с процессорами 386 DX & SX. Глава 14 - Введение в численные приложения : Предлагается обзор модуля чисел с плавающей запятой и пересматриваются понятия численных вычислений. Глава 15 - Архитектура числового блока : Описываются регистры для чисел с плавающей запятой и типы данных, доступные как для прикладных, так и для системных программистов. Глава 16 - Особые ситуации при вычислениях : Обсуждаются специальные значения, которые могут быть представленны в вещественных форматах процессора i486 - ненормализованные числа, нули, бесконечности, NaNs (нечисленные выражения) - так же, как и численные выражения. Эта глава в обязательном порядке должна быть прочитана системными программистами, но может быть пропущена программистами прикладными. Многие из описанных специальных ситуаций могут никогда не возникнуть в прикладных программах. Глава 17 - Команды работы с числами с плавающей запятой : Делается обзор команд, обычно используемых для численной обработки. Подробности конкретных команд отложены до Части V - справочника команд. Глава 18 - Численные приложения : Описывает арифметические возможности процессора i486 в вычислениях с плавающей запятой. Предлагает короткие примеры программ на ассемблере и языках высокого уровня. Глава 19 - Соображения системного уровня : Предлагается информация, интересная для разработчиков системного программного беспечения. Глава 20 - Примеры численного программирования : Предлагаются подробные примеры численного программирования на языке ассемблера процессора i486, включая условное ветвление, преобразование значений с плавающей запятой в их представления в формате ASCII и обратно, использование тригонометрических функций. 1.1.4 ЧАСТЬ

IV - Совместимость. Эта часть объясняет возможности архитектуры, которые поддерживают работу программ, написанных для более ранних версий процессоров семейства Intel. Естественный режим выполнения является обобщением среды процессоров 80286 и 386 DX. Все три режима выполнения поддерживают 16-разрядное программирование: 16 -разрядные команды могут быть выполнены в защищенном режиме, используя префикс размерности операнда, программы, написанные для процессора 8086 или в режиме прямой адресации процессора 80286 могут бять выполнены в режиме прямой адресации процессора 386 DX, и монитор виртуальной машины может быть использован для эмуляции режима прямой адресации с использованием виртуального режима 8086, даже в случае многозадачности с 32-разрядными программами. Глава 21 - Выполнение программ для процессоров 80286 и 386 DX : Объясняются различия в программировании для процессоров 80286 и i486, и между процессорами 386 DX и i486. Глава 22 - Режим прямой адресации : Объясняет режим прямой адресации процессора i486. В этом режиме процессор i486 работает как самые быстрые процессоры прямой адресации 80286 и 386 DX или как самый быстрый процессор 8086, усовершенствованный при помощи дополнительных команд. Глава 23 - Виртуальный режим 8086 : Описывает, как процессор i486 поддерживает выполнение одной или более программ для 8086, 8088, 80186 или 80188 в среде защищенного режима процессора i486. Глава 24 - Смешанный 16-разрядный и 32-разрядный код : Объясняет, как процессор i486 может смешивать 16-разрядные и 32-разрядные модули в одной программе или задаче. Каждый отделъный модуль может использовать одновременно 16-разрядные и 32-разрядные операнды и адреса. Глава 25 - Совместимость с арифметическими сопроцессорами 8087, 80287 и 387 DX : Сравнивает арифметику с плавающей запятой для процессора i486 с арифметикой арифметических сопроцессоров, используемых с ранними версиями процессоров семейства Intel. 1.1.5 ЧАСТЬ

V - Набор команд. Части I, II и III представляют читателю общие возможности множества команд с точки зрания того, как они соотносятся со специфическими особенностями архитектуры. Часть V описывает команды в алфавитном порядке, с теми подробностями, которые необходимы программистам, использующим язык ассемблера, и разработчикам отладчиков, компиляторов, операционных систем и т.д. Описание команды включает алгоритмическое описание операций, результаты установки флагов, эффекты аттрибутов размерности адресов и операндов и исключения, которые могут появиться в ходе выполнения команды. 1.1.6 Приложения. Приложения содержат таблицы кодирования команд и другие подробности в формате, разработанном для их быстрого поиска. 1.2 Дополнительная литература. Следующие книги содержат дополнительные материалы, связанные с процессорами

семейства Intel

: Introduction to the 80386, Order

Number 231252.

80386 Processor Hardware

Reference Manual, Order Number

231732. 80386

Processor System Software Writer's Guide, Order Number 231499. 80386 High-Performance 32-Bit CHMOS Microprocessor

with Integrated

Memory Management,

Order Number

231630. 376(TM) Embedded Processor Programmer's Reference

Manual, Order

Number 240314. 386(TM) DX Processor Programmer's Reference

Manual, Order

Number 230985. 386(TM) SX Processor Programmer's Reference Manual, Order

Number 240331. 80387

Programmer's Reference Manual, Order Number 231917.

376(TM) High-Performance 32-Bit Embedded Processor,

Order Number 240182.

386(TM) SX Microprocessor, Order Number 240187 Microprocessor and

Peripheral Handbook (vol.1),

Order Number 230843. The i486(TM)

Microprocessor Hardware Reference Manual аналогична данной книге и рекомендуется для использования разработчиками аппаратуры. Она содержит информацию, которая может быть полезной для программистов, особенно для системных программистов. Order Number 240552. The

i486(TM) Microprocessor Data

Sheet содержит самую

свежую информацию, касающуюся параметров устройств (уровни напряжения, время выполнения циклов шины, приоритеты одновременных исключений и прерываний и т.д.). Order

Number 240440. The i486(TM)

Microprocessor Product Brief Book

описывает множество различных продуктов, обычно используемых с ЦПУ i486. Order Number 240459. 1.3 Соглашения

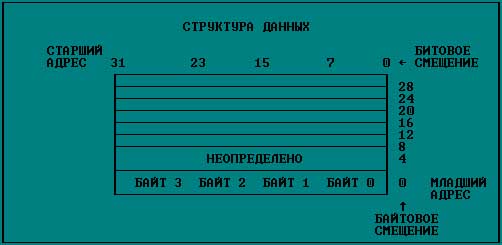

об используемых обозначениях Данное руководство использует специальные обозначения для форматов структур данных, мнемонического представления команд и шестнадцатиричных чисел. Обзор используемых обозначений упростит чтение данного руководства. 1.3.1 Порядок битов и байтов. В иллюстрациях размещения структур данных в памяти младший адрес располагается в нижней части рисунка; адреса возрастают по направлению к верхней части. Нумерация битов производится справа налево. Числовое значение бита равняется двойке в степени положения бита. Для процессора i486 нумерация байт в слове начинается с наименьшего значащего байта. Рисунок 1-1 иллюстрирует данное соглашение. Числа обычно представляются в десятичном виде (по основанию 10). Когда используется шестнадцатиричное число (по основанию 16), оно обозначается суффиксом 'H'.

Рисунок 1-1. Порядок Битов и Байтов. 1.3.2 Неопределенные биты и совместимость программного обеспечения. Во многих регистрах и дескрипторах некоторые биты помечаются как зарезервированные. Когда биты помечены как неопределенные или зарезервированные, важным для совместимости с последующими поколениями процессоров является то, чтобы программное обеспечение интерпретировало данные биты как имеющие в будующем свое значение, в данный момент неизвестное. Программное обеспечение должно руководствоваться следующими правилами, когда дело касается зарезервированных битов : - Независимость от состояния любого из зарезервированных битов при тестировании значений регистров, содержащих такие биты. Следует маскировать такие биты, прежде чем проводить тестирование. - Независимость от состояния любого из зарезервированых битов при записи в память или в регистр. - Независимость от возможности сохранить информацию, записанную в любом из зарезервированных битов. - При загрузке регистра, всегда необходимо загружать зарезервированные биты значениями, указанными в документации, если таковые имеются, или загружать их значениями, которые прежде хранились в том же регистре. ПРИМЕЧАНИЕ Зависимость от значений зарезервированных битов регистров делает программное обеспечение зависимым от неуказанного способа, при помощи которого процессор i486 управляет этими битами. Зависимость от зарезервированных значений приводит к риску несовместимости с будующими поколениями процессоров. ИЗБЕГАЙТЕ ЗАВИСИМОСТИ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ ОТ СОСТОЯНИЯ ЛЮБЫХ ЗАРЕЗЕРВИРОВАННЫХ БИТОВ РЕГИСТРОВ ПРОЦЕССОРА i486. 1.3.3 Операнды команд. Когда команды описываются символически, используется подмножество языка ассемблера процессора i486. В этом подмножестве команда имеет следующий формат : метка: мнемоническое обозначение аргумент1, аргумент2, аргумент3 где : - метка - это идентификатор, за которым следует двоеточие. - мнемоническое обозначение - зарезервированное название кода операции для класса команд, имеющих одинаковые функции. - операнды аргумент1, аргумент2, аргумент3 являются необязательными. В зависимости от кода операции может быть от нуля до трех операндов. Когда операнды есть, они имеют форму литералов или идентификаторов для обозначения данных. Идентификаторы операндов являются либо зарезервированными названиями регистров, либо предполагается, что они присвоены элементам данных, объявленных в другой части программы (которая может не быть приведена в примере). Когда в логической или арифметической операции указано два операнда, правый операнд является источником информации (операнд -источник), а левый операнд является местом сохранения результата (операнд-приемник). Некоторые ассемблерные языки расставляют источник и место хранения в обратном порядке. Например : 10LOADREG: MOV EAX, SUBTOTAL В этом примере LOADREG является меткой, MOV - это мнемоническое обозначение кода операции, EAX - место сохранения результата операции (приемник) и SUBTOTAL - исходный операнд (источник). 1.3.4 Шестнадцатиричные числа. Числа по основанию 16 представляются в виде строки шестнадцатиричных цифр, за которыми следует символ Н. Шестнадцатиричной цифрой является символ из множества (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F). Если число начинается с одной из цифр A-F, перед ним ставится нуль. Например, 0FH равняется десятичному числу 15. 1.3.5 Сегментная адресация. Процессор i486 использует побайтную адресацию. Это означает, что память организована в виде последовательности байтов и доступ к ней осушествляется как к последовательности байтов. Для доступа к одному или нескольким байтам, для адресации памяти используется его номер. Память, адресация которой может быть осуществлена таким способом, называется адресным пространством. Процессор i486 также поддерживает сегментную адресацию. Эта такая форма адресации, при которой программа может иметь много поименованных адресных пространств, называемых сегментами. Например, программа может хранить свой код (команды) и стек в разных сегментах. Адресация кодов всегда будет ссылаться на кодовое пространство, и адресация стека всегда будет ссылаться на стековое пространство. Ниже приведен пример обозначений, описываящий способ сегментной адресации: 10CS:EIP. Этот пример ссылается на байт внутри кодового сегмента. Номер байта храни- тся в регистре EIP. 1.3.6 Исключения (особые ситуации). Исключением называется событие, которое возникает, когда команда порождает ошибку. Например, попытка деления на ноль порождает исключение. Имеется несколько различных типов исключений, и некоторые из этих типов могут порождать коды ошибок. Код ошибки содержит дополнительную информацию об ошибке. Коды ошибок генерируются только для некоторых исключений. Пример обозначения, используемого для лдя иллюстрации исключения и кода ошибки, приведен ниже. #PF(код ошибки). Этот пример ссылается на исключение сбоя страницы при условии, что код ошибки указывает конкретный тип сбоя страницы. При некоторых условиях исключения, которые генерируют код ошибки, могут не иметь возможности породить верный код. В этом случае код ошибки равен нулю, как показано ниже : #PF(0).

[Назад] [Содержание] [Вперед] |